## 簡易 E S D 装置の開発とその適用検討 - E S D 破壊現象の特定 -

## 山崎規雄 真田 克

高知工科大学 工学部 電子・光システム工学科 〒782-8502 高知県香美市土佐山田町宮ノ口 185

E-mail: sanada.masaru@kochi-tech.ac.jp

あらまし ESD 耐量の調査と破壊防止を目的とした簡易な ESD 試験装置を試作した。装置は高電圧供給源とリレースイッチ及び、信号制御回路を有する。任意のモジュールを組込むことで代表的な 3 種類の静電気モデル(機械帯電モデル、人体帯電モデル、デバイス帯電モデル)を実現できる。この装置を用いて市販 LSI の耐量や故障解析用サンプル造りに利用する。又、入出力回路部の短絡箇所検出のための TLP 評価試験の適用を検討する。キーワード LSI 静電破壊 ESD 試験装置 信頼性 故障解析

# Development of Simple ESD Checker and it's Application - Detection of ESD destroy phenomenon -

Norio YAMASAKI Masaru SANADA

Department of Electronic and Photonic Systems Engineering, Faculty of Engineering, Kochi University of Technology First University Tosamayada, Kami-shi, Kochi, 785-8502 Japan E-mail: sanada.masaru@kochi-tech.ac.jp

**Abstract** Simple Electro Static Discharge(ESD) tester has been developed for evaluating ESD sensitivity of LSI and studying ESD protection of it. The tester system consists of high voltage power supply, relay switch, and signal control circuit. Representative three types of electro static mode: Machine model, Human body model and Charged device model, are built in the system. The tester is applied to measure ESD sensitive value of commercially LSI, to fabricate fault LSI with ESD damage, and to evaluate TPL test for fault portion detection of IN-OUT put circuit.

**Keyword** LSI, Electrostatic discharge(ESD), ESD tester, Reliability, Failure analysis

#### 1. はじめに

LSIの微細化に伴い、市場故障の約80%が外因的要因であり、その約70%がEOS、ESD破壊(以降、ESDと記載する)であることが報告されている(1)。リーク電流を伴うが規格値以内のため故障として顕在化しないLSIを含めるとこれらの割合はさらに増大し、信頼性の観点から大きな問題となっている。我々はこれまでにLSI故障に注力した解析技術や診断方式を検討してきた。前者は顕微鏡のよる外観解析とともに物理現象を検出する解析技術である。後者はI<sub>DDQ</sub>(論理の静止状態における電源電流)を用いた診断による故障箇所候補(2)や Tr 動作点解析を用いた故障箇所候補の特定方式(3)である。

これらの技術を用いて、我々は企業からの LSI の評価サービスを実施してきた。このような社会貢献にあって、解析結果が「ESD 破壊でした」というだけでは依頼企業へのアシストにはならず、発生の原因まで検

討した報告でなければ品質向上や信頼性向上に寄与しない。そのため、ESD 試験装置を自作し、発生原因を提案することで貢献への高度化を計画した。

## 2. これまでの経緯

これまで解析依頼を受けた故障 LSIの 60% は入力端子近辺の破壊であり、その内 75% は光学顕微鏡を用いた外観検査で ESD 破壊箇所を確認できた。しかしながら、残り 25% は入力特性がリークを伴いながらも異常個所を確認できないモードであった。このため、故障に伴う発熱や発光現象を利用することで故障箇所を特定するための工夫や装置開発を行ってきた。前者は古くから利用されている液晶塗布法によるホットスポット検出であり、後者はエミッション顕微鏡(EMMS)による解析がある(4)。特に EMMS 装置に関して冷却CCD と近赤外用対物レンズを用いて 1100nm までの発光を検出できる装置を自作した(5)。そしてこれらの装

置を用いることで異常個所を特定することが出来るようになった。しかしながら、ESD 破壊の原因を明らかにするに到っていないため発生原因を提案すべく ESD 試験装置を自作するに到った。本論文はこの ESD 故障と試験装置の自作内容まとめたものであり、第2章にてこれまで解析した ESD 破壊による故障事例を示す。第3章にて自作した ESD 試験装置の構成を、第4章にてその適用検討に関して示し、最後にまとめを行なう。

## 3. ESD 破壊の解析事例

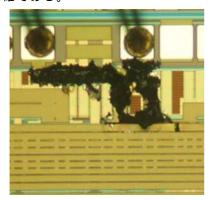

ESD 破壊は入力端子の V-I 特性よりリーク電流やオープン故障の特定から判断できる。しかし、パッケージ開封後の外観検査にて痕跡を検出できるものとできないものがある。図 1 は前者の事例であり ESD 破壊の痕跡は明確である。

#### 図1 光学顕微鏡による ESD 破壊箇所の検出事例

後者は異常電流に伴う発熱や発光現象を特定することで検出できる。発熱は液晶塗布法と呼ぶ方式で、LSI表面に形成した液晶薄膜において発熱に伴う液晶の相転移や回転ゆらぎからビジュアルに特定できる。図1は解析結果であり、プロービングによる信号供給にて故障箇所を特定した。

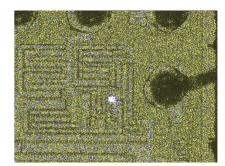

図2 液晶による発熱箇所の検出事例

発光は PN 接合面での破壊に伴う現象であり逆励起 光や熱による発光現象である。図3は自作した冷却 CCD(検出帯域 max 側~1100nm)を用いたエミッショ ン光解析により検出した例である。

図3 発光箇所の検出事例検出

以上、ESD 起因による故障箇所は故障痕跡は簡単に検出できるようになったが、この発生原因は多様であり破壊形状と静電気パルスのエネルギー関係からこれらの識別を行なうことで再発防止や信頼性向上を図る必要がある。そのため、ESD 試験装置を用いた再現実験が必須となる。以下のこの装置を自作したのでこの経緯を述べる。

#### 4. ESD 試験装置の構成

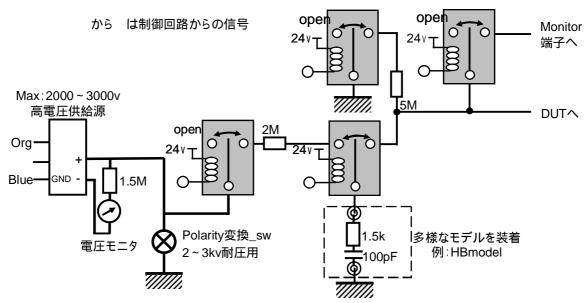

装置は代表的な3つの故障モデルをLSIに印加し、これらの耐量や破壊状況を知ることを目的としている(6)。図4に試作した装置写真を示す。高電圧を扱うために装置全体をBOXに搭載し、フタをした状態で試験するため、パルス経路はBOX表面のランプにて識別できるようになっている。又、電源はフューズを介して印加させている。ESD試験装置は3つの回路から構成される。1つは高電圧パルス供給するパルス信号を受けたリレースイッチの開閉によりESDパルスをLSIに供給するの回路である。3つ目はESDモデルを形成する回路である。この回路は付け替えによる所望のESDパルスを発生させることができる。通常、数nsに数千ボルトのパルスが印加する形態の波形を準備するために抵抗(R)と容量(C)での組合せでモデルを構成する。

図4 試作した ESD 試験装置

図5 信号伝搬経路

図5は信号伝搬経路図である。経路は図に示すように至って単純である。高電圧源から供給される所望の電圧を ESD モデル回路へ印加し、あるタイミングでLSIへ供給する形態である。ESD モデル回路は交換することができる。伝搬経路において高電圧電源の電圧モニタと ESD モデル波形をモニタする端子を準備している。

## 4.1. パルス信号制御回路

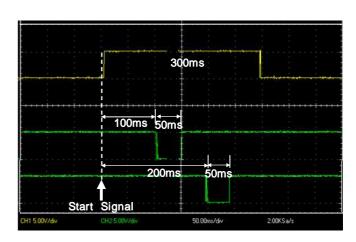

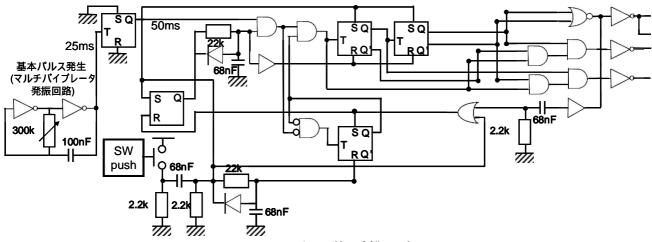

図6はパルス信号のタイミング波形を、図7は制御回路を示す。回路は大きく3つに分かれており、25msの基準パルスを作成するマルチバイブレータ発振回路、各タイミングでパルスを制御する回路及び、出力回路である。出力する信号はトリガー信号対して5つのパルスを発生する。端子 、 は駆動時間300msを保障するタイミングでありこの間でLSIにパルスは印加される。 はLSIへのESDモデル回路に入力した電圧をモデルに依存したパルスでありLSIへ印加するタイミングである。 は信号経路をGNDにするタイミングであり、パルス印加から100ms後の50ms間に設定する。

#### 4.1.1. パルス発生のタイミング設定留意点

パルス発生のタイミングはリレーの応答や内部ノードの電位が安定する時間を考え 50ms に設定する。ESDサージは数パルス印加するがそのパルスとパルスの間を数百 ms とする。この理由は 2 点あり、1 つはESD試験パルスを保護回路に注入した際に熱が発生するためである。その熱が拡散する前に次のサージを入れるとLSIの ESD 耐量の低下や値のバラツキが生ずる

ためである。もう 1 点はデバイスに帯電した残留電荷を抜く時間が必要となるためである。今回この試験装置は昇圧回路の負荷能力があまりないため、立ち上がり時間を数 ms を見込んでいる。

図 6 タイミング波形

#### 4.2. ESD パルス供給回路

2つ目の高電圧がESDモデル回路により印加する回路であり、高電圧 3000V(at max0.5W)の信号が装置内を伝搬するため、高耐圧用電子部品(配線、接続端子、抵抗、容量など)及び、フューズとBOX内への装着を行なった。高電圧ESDパルス形成回路へ導かれる基準電圧に対するモデルを正/負に使い分けて供給するために極性変換スイッチ(Polarity Transferswitch)による表に示すように4条件の信号を形成する。

Vss 基準に対するプラス(+)サージ、マイナス(-)サージ、 Vcc 基準に対するプラス(+)サージ、マイナス(-)サージ、

図7 パルス信号制御回路

である。

これらのサージ電圧は数百 ms 以上のインターバルで3回から5回加えられる。ESD モデルのパルスはリレーを介して LSI へ印加させが、この印加は可能な限り寄生成分(R,L,C)を除いた印加が必須である。このためリレースイッチは水銀リレーを用い、さらに LSI との結線距離を極力短くする必要がある。

#### 4.3. ESD モデル

ESD モデルは Machine model (MM:機械帯電モデル)、 Human body model (HBM:人体帯電モデル)、 Charged device model (CDM:デバイス帯電モデル)の3種類を準備している。これらの基本構造は図8に示すような抵抗(R)とコンデンサー(C)の直列回路構成で統一してある。そして、その回路を図6に記載したSW 下に装着することで形成が可能になる。今後、SW 切り替えによりこれらの自動測定を行なう改善を計画している。以下に各モデルを簡単にまとめる。

図8 ESDモデルの基本構造

## 4.3.1. 機械帯電モデル(MM)

Machine model (MM:機械帯電モデル)は帯電した 金属が LSI 端子に接触したとき放電する現象のモデル である。この現象の再現は 200pF のコンデンサー (C) を介しての直接放電にて実施する(R=0)。そのため、 準備するモデルは図に示すように高耐圧に耐える 200pF を準備する。印加電圧は 300V から 500V と比較

的低い電圧を準備する。等価回路は直列抵抗を含まないのでその放電特性は短い時定数を示す。

## 4.3.2. 人体帯電モデル(HBM)

Human body model (HBM:人体帯電モデル)は人体に帯電した静電気が LSI 端子に接触したとき放電する現象のモデルである。この現象の再現は 100pF のコンデンサー(C) からの 1.5k の抵抗(R)を介した放電にて実施する。印加電圧は 2kV から 5kV の高い電圧を準備する。そのため、準備するモデルは図に示すように高耐圧に耐える 100pF と 1.5k を準備する。

## 4.3.3. デバイス帯電モデル(CDM)

Charged device model(CDM:デバイス帯電モデル)は帯電した LSI の端子が金属や治具類に触れたとき放電する現象のモデルである。このモデルは立上り時間が速いため保護回路より内部回路内への進入が起こりやすくゲート酸化膜破壊といった電界破壊がおきやすい傾向にある。この現象の再現に対して、上記の放電を擬似的に行なうために今回 5pF から 20pF のコンデンサー(C)から数 の抵抗(R)を介した放電にて実施する。印加電圧は 1kV から 10kV と広範囲に振っている。

以上、ESD 試験装置の構成とその要点に関して述べた。

#### 5. 適用検討

本装置の適用に関して述べる。ESD 破壊はこの発生 箇所を特定できても、この発生原因が明確にならない 限り LSI や製造への歩留まり向上につながらない。こ のためどのようなパルスが検出された故障に対応する か再現実験を行う必要がある。上記したように現在 3 つのモデルを準備している。これらの印加による破壊が同一精度で再現できれば特に LSI の取扱い過程への改善提案が可能となる。

もう 1 つは TLP(Transmission Line Pulse Method)と呼ぶ 擬似的な ESD パルス幅の変化に対応した破壊箇所の 回路位置を評価する試験方法である。ESD モデルと LSI に到る経路制御によりこの試験が可能となる。

## 6. まとめ

ESD 耐量の調査と破壊防止を目的とした簡易な ESD 試験装置を試作した。装置は高電圧供給源とリレースイッチ及び、信号制御回路を有する。任意のモジュールを組込むことで代表的な3種類の静電気モデル(機械帯電モデル、人体帯電モデル、デバイス帯電モデル)を実現できる。

この試作過程において色々な問題点が明らかになった。1つは ESD パルスを LSI に印加するまでの経路の問題であり、寄生素子の低減策を再検討している。もう1つは電源の極性変換スイッチの問題である。このスイッチに関しては独自の設計による設置を計画している。特性精度の向上のために不可欠の部品である。これらの知見は ESD を理解する上で貴重なノウハウとなった。

そのため、現在のところ完全な動作確認に到って いない。今後の研究会において試作した試験装置 を用いた適用事例を改めて報告する予定である。

#### 謝辞

ESD試験装置の試作に対してご指導頂きました富士 通㈱の伊藤誠吾様に深くお礼申し上げます。又、装置作成において多岐に渡りご指導頂き、構成上のアドバイスを頂いたセブンエイト製作所:山崎章男様にお礼申し上げます。

##

- [1] 今井康雄,田中大起,"電子部品の故障解析および 良品解析 - 車載用電子部品の信頼性向上のため の取り組み - ,"信学技報 R2007-29~36, Vol. 107, No. 213, pp.35-39, Sept.2007

- [2] 真田克、植平和正,布施英悟、"IDDQ を用いたロジック LSI 製造工程における欠陥もモードの分類 ," LSI テステイングシンポジウム 2000, pp.88-93.

- [3] 真田克, "トランジスタ動作点の解析による故障 論理の追跡," LSI テステイングシンポジウム 2006, pp.205-210.

- [4] 二川清, "LSI の故障解析手法とその動向," LSI テステイングシンポジウム 2001, pp.187-192.

- [5] 有田竜一,橋田啓示,真田 克,"故障 LSI のための 簡易発光検出装置の開発,"2007 電気関係学会四 国支部連合大会、9-15, p.94,Oct 2007.

- [6] 日本電子機械工業会規格, "半導体デバイスの静 電 破 壊 試 験 方 法 , "EIAJ EDX-4701(1991), 4702(1994)