# スイッチングレベルシミュレーションを用いた組合せ回路内故障箇所の特定 Fault diagnosis technique for combinational circuit blocks using switching level simulation

真田 克、 則松研二

M. Sanada, K. Norimatsu

半導体理工学研究センター・設計技術開発部・テスト設計開発室 Design for Test Group, Design Technology Development Department Semiconductor Technology Academic Research Center

要約: LSI を構成する基本的論理であるセルの故障診断方式を開発したので報告する。診断対象とするセルは組合せ回路である。診断はレイアウト情報を用いて IDDQ 故障が発生する可能性のある箇所を故障候補として抽出し、その後、これらの候補を回路に埋め込むことでスイッチングレベルシミュレーションを実施する。そして出力された論理と実際の出力論理値と一致する候補を確度の高い故障候補として特定する方式である。

Abstract: The fault diagnosis technology has been developed to detect the fault portions in cell circuit, composing LSI. The cell circuit for the diagnosis is combinational circuit. The diagnosis is first to select the candidate fault portions that may bring abnormal  $I_{DDQ}$  based on layout information, to implant in the candidate fault portions in the circuit, and then to detect the OUTPUT logic value by using switching level simulation. The candidate fault portion is decided as high reliable fault portion of which logic result synchronizes exactly with real output logic state.

キーワード: スイッチングレベルシミュレーション、組合せ回路、故障診断、論理故障、I<sub>DDQ</sub>故障 Keywords: switching level simulation, combinational circuit, fault diagnosis, logic fault, I<sub>DDQ</sub> fault

# 1. はじめに

LSI の大規模化、多層配線構造化は故障箇所の特定を困難にしてきており、故障解析は膨大な工数を費やす傾向になってきている。このため故障診断と呼ぶ、ソフトウエアを用いて故障箇所候補を特定し、その候補に対して物理解析を行う方式が主流になってきている。

故障を指摘する情報には論理情報と電流情報とがあるが対象とする情報において診断方式が異なる。前者の診断には異常となる出力期待値を起点にして出力から入力方向へ逆論理展開し故障候補を検出する方式や、故障を埋め込むことでシミュレーションを行い出力する論理と故障論理の一致から故障候補を特定する方式がある(1)。

後者の診断に対しては電流異常が物理欠陥の存在を指摘するシグナルであることを利用して異常電流が流れる論理パターンを用いて故障候補を特定する方式<sup>(2)</sup>や、故障を埋め込むことでシミュレーションを行い電流異常の発生を確認し故障候補を特定する故障モデル方式<sup>(3)</sup>がある。

しかしながら、従来、これらの診断はセル間を 接続する配線に対して故障候補を特定する方式 であり、セル内エレメントに対する故障に関しては 診断がなされていなかった。セル内診断がなされていなかった理由は3点ある。

セルの回路規模(Tr 数)が小さいものが多かったため、マニュアルによる故障箇所の絞込みで対応できたためである。

素子認識の違いのためであり、セル単体が論理素子と見なせるのに対して、セル内トランジスタ(Tr)はスイッチング素子のため同一レベルで論理シミュレーションによる対応ができないためである。

レイアウト認識の違いのためであり、セル間ネットがセグメント記載であるのに対してセル内ネットはポリゴン記載のためデータの取り扱いにおいて連続性を伴わないためである。

しかし、今日の LSI の進展はセルと言えども Tr 数は 500 個を超える規模もありマニュアル対応が困難になってきており、上記のセル間とセル内のデータ構造の違いを解決することで診断方式を開発する必要にせまられてきた。今回、セル内故障箇所を特定する方式を開発したので報告する。

2章ではセル内診断のコンセプトについて2種類のデータを参照して説明する。3章にてスイッチング素子としてのTrを用いた論理シミュレーシ

ョン方法について、4章にてレイアウト情報の特定 方式について、5章にて診断フローの概要とその 診断事例について、そして最後にまとめを行う。

# 2. セル内診断のコンセプト

セル内診断の基本的考え方について述べる。 ここでセル内故障候補の検出感度の向上のため に論理故障と電流故障の相関データ及び、電流 故障が示す故障モードの分類データを参照した。

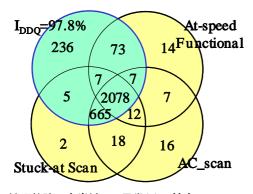

前者は ITC2000 にて P.Maxwel が発表した自社製品に対して実施した 4 つのテスト( $I_{DDQ}$  テスト及び、3 種類の論理テスト: At-speed Function, AC-Scan, Stuck-at Scan)に対して選別された 3140 個の故障 LSI の内訳である。その結果は  $I_{DDQ}$  故障が論理故障品の 97.6%、さらに全体の故障品の 97.8%とほぼ故障品全体を占めていることを示している。ここで LSI は 0.35  $\mu$  m, 3 層配線、3.3V 駆動品の ASIC 品であり、 $I_{DDQ}$  規格は 50  $\mu$  A(1327vectors with 81% persude-stuck-at coverage) である。図 1 にその結果を示す $^{(4)}$ 。

論理故障の大半はI<sub>DDQ</sub>異常として検出:97.6% (故障全数に占めるI<sub>DDO</sub>故障の割合:97.8%)

図 1 選別された 3140 個の故障 LSI の内訳<sup>(4)</sup>

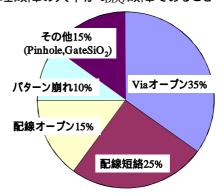

後者は MicroElectronics& Reliability 1995 にて M.Sanada が発表した  $I_{DDQ}$  異常品の故障解析結果からの故障モードの分類データである。対象とした LSI は最大 3 層構造品で、液晶塗布法を用いた解析結果である。このデータから Via オープン故障 35%、配線短絡故障 25%、配線オープン故障 25%と全体の 75%が配線系故障で占められていることを示している。図 2 にその分類内容を示す $^{(5)}$ 。そして、今日の $^{(5)}$ 0 層構造に至る多層配線構造化した LSI において  $I_{DDQ}$  故障が占める配線系の割合はさらに増加しているもの考える。

以上のデータは 論理故障の大半が Ippo 故障であること

図 2 I<sub>DDO</sub> 故障解析結果からの故障モードの分類<sup>(5)</sup>

I<sub>DDQ</sub>故障の 3/4 以上は配線系の故障(Via-open、配線-short、配線-open)であること

を述べている。これらのデータをもとに、主にセル内の配線系に対する故障診断方式を検討した。 又、診断対象とする回路は組合せ回路に限定した。この理由は同一の入力テストパターンで論理故障と I<sub>DDQ</sub> 故障が同時に発生するためであり、論路故障と I<sub>DDQ</sub> 故障の両方を満たす箇所を故障候補として識別することで精度良〈故障候補を特定できるためである。I<sub>DDQ</sub> 故障箇所の検出に関しては I<sub>DDQ</sub> 故障を発生する可能性のあるレイアウト構造からその箇所を決定することで故障候補を特定する。診断はこの故障候補箇所を回路に埋め込み、スイッチングレベルシミュレーションを実施することで、出力する結果が実際の故障と一致する箇所を故障候補として特定する方式である。

# 3. スイッチングレベルシミュレーション

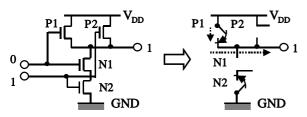

スイッチングレベルシミュレーション(Switching-level Simulation: SLS 又は、Sw-L-S と記す)は複数の Tr にて構成された回路の論理をシミュレーションするためのツールである。方式は Tr のゲート端子(G)に印加する論理に同期してソース(S)・ドレイン(D)間が導通または非導通となるスイッチング動作をベースとすることで、回路全体の接続関係から各ノードの論理を特定する方式である。

2 入力 NAND 回路を用いた SLS による論理の 識別を説明する。図 3 は入力論理(In1,In2)に (0,1)が入力したときの論理の識別の説明図であり、 PchTr1(P1)、NchTr(N2)はS-D 間がスイッチし、導 通状態となり P2,N1 は OFF 状態となる。従って、 出力端子には V<sub>DD</sub> から P1 を介して "1"が出力する。同様に(In1,In2)に(1,0)が入力したとき出力端子には V<sub>DD</sub> から P2 を介して "1"が出力し、(In1,In2)に(0,0)が入力したとき出力端子には P1及び、P2 が導通し "1"が出力し、(In1,In2)に(1,1)が入力したとき出力端子には N2,N1 が導通状態となり GND 電圧が出力し"0"として認識される。

図3 2入力 NAND 回路の SLS

SLS を実施するための Tr と配線間の接続情報は SPICE (Simulation Program with Integrated Circuit Emphasis) データから取り出す。図 4 は一般的な SPICE データであり矩形で囲った箇所がシミュレーション用データとして認識され、論理テーブル(LT)として用いられる。LT は横軸に Tr の4つの端子(S:Source,G:Gate,D:Drain,B:Base)を、縦軸に Tr 名を表示したテーブルである。電源の識別は PchTr は VDD 方向を、NchTr は GND 方向を S 端子として識別することで、SPICE 記述が一定でなくても Tr 間の接続関係から Sと D 端子を自動的に識別できるようにした。

| *       |      |             |     |           |        |            |        |

|---------|------|-------------|-----|-----------|--------|------------|--------|

| .SUBCKT |      | XOR2 A B    |     | Z VDD GND |        |            |        |

| **MACRO |      | VERSION 3.0 |     |           | Oct-04 | 2004_10_14 |        |

| MN1     | GND  | Α           | A01 | GND       | NENHHP | L=0.50U    | W=9.0U |

| MN2     | A03  | В           | A02 | GND       | NENHHP | L=0.50U    | W=4.5U |

| MN3     | GND  | A01         | A03 | GND       | NENHHP | L=0.50U    | W=4.5U |

| MN4     | GND  | A02         | A04 | GND       | NENHHP | L=0.50U    | W=9.0U |

| MN5     | GND  | A10         | A06 | GND       | NENHHP | L=0.50U    | W=9.0U |

| MN6     | GND  | A04         | A06 | GND       | NENHHP | L=0.50U    | W=4.5U |

|         |      |             |     |           |        |            |        |

| MP8     | VDD  | В           | A07 | VDD       | PENHHP | L=0.50U    | W=9.0U |

| MP9     | VDD  | Α           | A09 | VDD       | PENHHP | L=0.50U    | W=9.0U |

| MP10    | VDD  | A07         | A09 | VDD       | PENHHP | L=0.50U    | W=9.0U |

| MP11    | VDD  | A09         | A10 | VDD       | PENHHP | L=0.50U    | W=9.0U |

| .ENDS   | XOR2 |             |     |           | 1      |            |        |

図4 SPICE データから抽出した論理テーブル(LT)

#### 4.レイアウト情報による故障候補の特定

セル内のレイアウト情報は LVS(Layout Versus Schematic)による検証が一般的に行われている。 そして、LVS 結果からセル内のレイアウト情報を、 セル間のレイアウト情報と対応付けて抽出するこ とができる。この情報を用いて I<sub>DDQ</sub> 故障となる可能性のあるレイアウト構造の特徴を有する箇所、隣接ネット対、交差ネット対及び、Via と Via を介した配線が接続する Tr のデータを取り出す。

データ抽出のためのアプローチは 2 つある。1 つは LSI 全体から注目するセルのデータを取り出すアプローチであり、もう1 つはセルを指定し、直接データを取り出すアプローチである。前者は既存の診断ツールにて特定された複数セルにて組み合わされた回路規模をベースとして、この回路内の各セルに対してデータを取得する方式である。LVS は階層 LVS に限定しているため、配線のインスタンス名は LSI 全体として付けられている配線名と下に各セル内の配線のインスタンス名は ASI 全体として定義される。後者はセル毎の LVS 結果を用いてレイアウトとインスタンス名の対応を取ることでデータを取得できる。

以上の識別後、隣接ネット対、交差ネット対及び、ViaとViaを介した配線が接続するTr名を取り出す。これらのデータは診断フローのレイアウト 故障候補リストファイル【.sfc】に収納される。

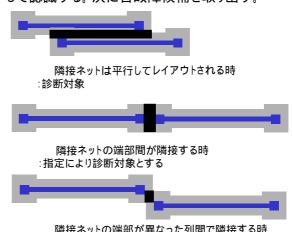

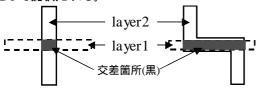

# 4.1 隣接ネット対、交差ネット対候補の特定(6)

隣接ネット対、交差ネット対に関しては、セル毎に LVS データベースからネットのポリゴン情報を取り出し、その矩形座標列をそのまま DEF 形式として認識する。次に各故障候補を取り出す。

隣接ネットの端部が異なった列間で隣接する時:指定により診断対象とする

薄灰色部 :隣接部に影響を与えるエリア

中灰色部 : パターン形状 黒色部 : 診断対象エリア

図 5 隣接ネット対のレイアウト構造

【隣接ネット対】

図 5 に隣接ネット対としてのレイアウト構造を示す。3 種類の形状を取得する。

隣接ネットが並行してレイアウトされている場合であり、任意の間隔以内の重なり部が診断対象領域となる。

隣接ネットの端部間が隣接した場合であり、この間の重なり部を診断対象とする。

隣接ネットの端部が異なった列間で隣接する場合であり、任意の間隔以内の重なり部を診断対象とする。

#### 【交差ネット対】

図 6 に交差ネット対としてのレイアウトを示す。 上下配線層間の重なり箇所の存在がが交差ネット対として認識される。

図 6 交差ネット対のレイアウト構造

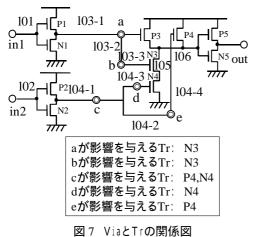

# 4.2 Via を介した Tr の特定

Via 及び、Via を介した配線が接続する Tr のデータはViaオープン故障箇所を特定するために用いられる。Via を介した Tr の特定に関して図7を用いて説明する。

図中、配線 103 に注目した時、103 は 3 つのセグメント(103-1、103-2,103-3)に分かれている。103-1 は P1,N1 からの出力配線が P3 の B 端子に入力している。同時に中間にて Via「a」を介して 103-2 に分岐している。さらに、103-2 は Via「b」を介して 103-3 に接続され、N3 の B 端子に入力している。

この場合、Via「a」の導通状態が影響を及ぼす Tr は N3 であるため、a が影響を与える Tr を N3 として識別する。同様に、Via「b」は b が影響を与える Tr を N3 として識別することで、Via と Tr の関係を認識するようになっている。同様に、Via「c」は c が影響を与える Tr:P4,N4 を識別し、Via「d」は d が影響を与える Tr:N4 を識別し、Via「e」は e が影響を与える Tr:P4 を識別する。

#### 5.診断フロー

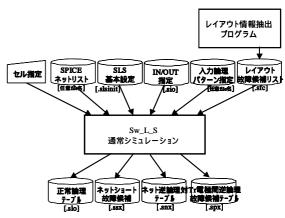

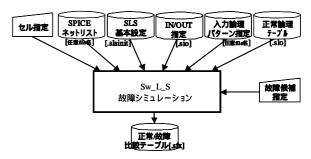

セル内故障特定のための診断フローの概要を 説明する。フローは2段に分かれる。

1段目は診断データの作成フローであり図 8 にフローを示す。入力データは【セル指定/SPICE ネットリスト/SLS 基本設定/IN\_OUT 指定/入力論理パターン指定/レイアウト故障候補リスト】である。これらのデータを用いて SLS を行う。その結果、【正常論理テーブル/ネットショート候補/ネット逆論理テーブル/Tr 電極間逆論理テーブル】が出力する。但し、Viaオープン故障箇所候補はすべてが診断対象となるため出力はなされない。

図81段目の診断データの作成フロー

# 2 段目は故障モードに依存した故障候補の特

定フローであり、図9にそのフローを示す。 図92段目の故障候補の特定フロー

vdd 3.3L 電源電圧 th 1.5 しきい電圧指定 power VCC VDD 電源ピン指定 gnd GND 接地ピン limit 20 発振制限回数

入力データは【セル指定/SPICE ネットリスト/SLS 基本設定 /IN\_OUT 指定/入力論理パターン指定/正常論理テーブル/故障候補指定】である。これらのデータを用いて SLS を行う。SLS はレイアウト情報を用いて特定されている故障候補を回路中に埋め込み、論理検索する故障シミュレーションである。診断結果、【正常/故障比較テーブル】が出力する。この結果を用いて実際の論理故障と一致する候補を特定する。

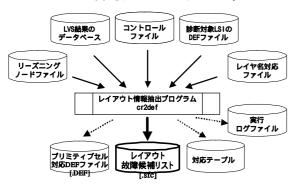

1 段目の診断において記述した「レイアウト故障候補リスト」について説明する。リストはレイアウト情報から抽出したデータである。図 10 に示すフローは LSI 全体からのデータ抽出である。セルに限定した時は直接候補を抽出することでリストを作成する。入力データは【リーズニングノードファイル/LVS 結果のデータベース/コントロールファイル/DEF/レイヤ名対応ファイル】である。これらの

データを用いてレイアウトに起因する故障箇所候補を検索する。検索結果として【セル対応 DEF ファイル/レイアウト故障候補リスト/対応テーブル/実行ログファイル】が出力する。この「レイアウト故障候補リスト」が診断用データとして用いられる。

図 10 レイアウト故障候補リストの取り出しフロー

#### 5.1 入力データの説明

上記したフローにおける各入力データについて説明する。

- \*セル指定:診断対象セルの名称である。

- \* SPICE ネットリスト【 】:解析を行うライブラリセ

ルの SPICE ネットリストファイルである。

- \*SLS 基本設定 [.slsinit]: SLS のための基本情報を記述するテキストファイルである(表参照)。

- \*IN\_OUT 指定【.sio】: セルの入力および出力端 子の属性を指定するテキストファイルである。

- \* 入力論理パターン指定【-】: 入力信号を指定 するテキストファイルである。未指定の場合、全 ての入力論理の組合せが対象となる。

- \* レイアウト故障候補リスト [.sfc]: レイアウト情報 抽出プログラムから出力されるテキストファイル である。隣接、交差ネットと Via が影響する Tr 名が記述される(表参照)。

adjoin net1 net2 隣接 cross net1 net3 交差 Via1 Tr1 Tr2 Viaを介したTr名

- \* コントロールファイル: レイアウト情報抽出プログラム実行に関する各種パラメータおよびビアセル情報の記述ファイル(ビアセル情報/隣接ネットチェック条件/LVS 結果データベースのパス/ATTACH レイヤ情報)である。

- \* 故障候補指定:診断対象とする故障モードの 指定であり、ネット間ショート故障 / Tr 電極間ショート故障 / Via オープン故障候補のファイル 指定 [.sfc] を行う。 さらに個別対応として任意の 故障を診断できる。

# 5.2 出力データの説明

上記したフローにて出力する出力データについて説明する。

- \* 正常論理テーブル【.slo】: 入力論理パターンに おける各内部ノード及び外部出力ピンの論理 値を出力したテキストファイルである。

- \* ネット逆論理対テーブル [.snx]: 入力論理パターンにおける、逆論理となるネット対を「\*」の印で表したテキストファイルである。

- \* ネットショート故障候補[.ssx]: レイアウト情報抽出プログラムから出力される隣接、交差ネット対リスト中、逆論理となる対の出力ファイルである。

- \* Tr 電極間逆論理テーブル [.spx]: 入力論理パターンにおける各 Tr 電極端子に対し、逆論理となる対を「\*」の印で表したテキストファイルである。

- \* 正常/故障比較テーブル【.sfx】: 故障シミュレーション結果と正常シミュレーション結果と比

較し、期待値の出力信号(L,H,Z,X)と異なる 出力論理値を表示分けする。その他の出力 は正常論理テーブルファイルと同様である。

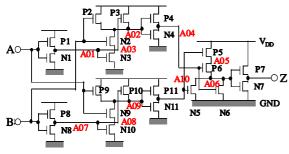

#### 5.3 診断事例

診断事例は図 11 に示す Exclusive-OR 回路である。まず、 $I_{DDQ}$  異常を伴うと考えられる故障候補をレイアウト情報を用いて取り出す。故障モードは隣接ネット、交差ネット及び、Via を属性にもつ Trであり、レイアウト故障候補リスト [.sfc] が作成される。これらのデータを回路に埋め込み SLS を行い、出力論理値を特定する。例示の故障候補は A10と A05 間に短絡を仮定した時の診断結果である。図 12 は故障診断の SLS 処理過程の出力リストであり、図 13 は診断結果である。

図 11Exclusive-OR 回路図

Starc% sls XOR2.spice X2 -short A10 A05 [Fault Simulation <short net>]

>>> Read Netlist(XOR2.spice)...

**INIT OK**

Read Netlist OK

>>> Read Pin Type(XOR2.sio)...

Read Pin Type OK

>>> Circuit Data

[Pin Type] Vdd: VDD

Gnd: GND In: AB

Out : Z

[Voltage] Vdd : 3.300000 Vth :

1.500000

$R = Vth \implies 1$

>>> Merge Netlist...

Merge Netlist OK

>>> Set Tr Polarity...

Set Tr Polarity OK

>>> Set Wired...

Set wired count: 8

Set Wired OK

>>> Find Loop Net...

A circuit is a loop type!

Find Loop Net OK

>>> Simulation start...

SignalPattern: 4 Times of Simulation: 1

\*Warning: Feedback circuit is oscillating.

Simulation OK

図 12 故障診断の処理過程の出力リスト

図13 診断結果

# 6.まとめ

LSI を構成する基本的論理であるセル(組合せ回路)の故障診断方式を開発している。診断はレイアウト情報を用いて IDDQ 故障が発生する可能性のある箇所を故障候補として抽出し、その後、これらの候補を回路に埋め込むことで SLS を用いてセルの出力端子に出力する論理を特定する方式である。その結果、実故障論理と一致する候補を高い信頼度で特定することができる。

本研究は半導体理工学研究センタにおける故障診断プロジェクトの 1 つであり、参加企業の支援のもとに研究開発している。

# 参考文献

- [1] 久慈憲夫、"故障診断手法とその動向"、LSI テスティングシンポジウム / 2000 会議録、pp.64-69 (2000).

- [2] M.Sanada and H. Fujioka, "A CAD-Based Approach to Fault Diagnosis of CMOSLSI with Single Fault Using Abnormal I<sub>DDQ</sub>," IEICE Trans. Fundamentals., vol. E80-A, no. 10, pp. 1945-1954 (1997).

- [3] R.C.Aitkin, "A Comparision od Defect Models for Fault Location with I<sub>DDQ</sub> Measurement," in Proc. IEEE International Test Conference, pp. 778-787 (1992).

- [4] P.Maxwell, I.Hartanto and L.Sentz, "Comparing Functional and Structural Tests," in Proc. IEEE International Test Conference, pp.400-407 (2000).

- [5] M.Sanada, "Evaluation and Detection of CMOS-LSI with Abnormal I<sub>DDQ</sub>," Microelectronics and Reliability, Vol.35, No.3, pp. 619-629 (1995).

- [6] M. Sanada, "Layout-Based Detection Technique of Line Pairs with Bridging Fault Using I<sub>DDQ</sub>," IEICE Trans. Fundamentals, Vol. E87-D, No.3, pp.557-563 (2004).

連絡先

連絡先氏名 真田 克

所属機関 半導体理工学研究センター・設計技術

開発部・テスト設計開発室

所在地 〒222-0033 横浜市港北区新横浜 3-17-

2 友泉新横浜ビル 5F

電話/FAX 045-478-3238/045-478-3299

E-mail sanada@starc.or.jp