MOS FET (Metal Oxide Semiconductor Field Effect Transistor)

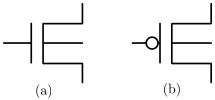

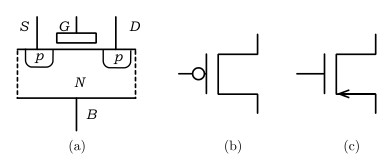

シリコン基板とシリコン酸化膜(SiO2)上のゲート電極の間の電界によりチャネルを作り,ソースとドレイン間の 電流を制御する素子.MOSはゲート電極(M),酸化膜(O),基板(S)をあらわす(図1,図2). この素子は4端子の素子であるが,LSI内部で使用される場合は基板電極をグランドまたは電源に接続することが多いので, 基板電極を省略することもある. 基板電極はサブストレート,バックゲートなどと呼ばれ,sub,Bなどと表記される.

MOS FETにはゲート・ソース間電圧が0のときにドレイン電流のながれないエンハンスメント(Emhancement)型と ゲート・ソース間電圧が0のときにドレイン電流の流れるデプリション(Depletion)型があるが,実際に使用されるのは大部分がエンハンスメント型である.

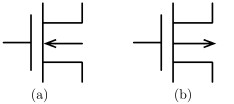

図1(b),図2 (b)の記号は, 基板電極を省略し,Pチャネルのゲートには丸を描くことでNチャネルとPチャネルの区別をつけている. 図1(c),図2 (c)の記号は,ソース・基板間のPN接合を矢印で表したものである. いずれの記号もLSI内部の回路を記述するためにも用いられるものである.

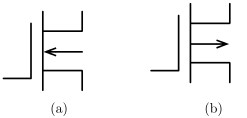

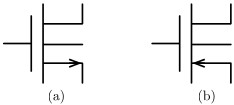

MOS FETは電力用や高周波回路用を除くと単独の部品として使用されることがまれであり, LSI内部の素子ではソースとドレインの構造が対称であることが多いため,ソースとドレインの区別を表示しない記号が用いられることが多い. これらの記号はすべてエンハンスメント型であり,デプリション型の素子を記述する場合は Dep.などと別記するか,チャネル部分(縦棒)を太くした記号などが用いて区別をする.

バリエーションは基板電極の記述方法,ソースとドレインの区別の方法により生じている. 図3(a),(b)は,図1(b),図2(b)に基板電極端子を加えたもの. 図4(a),(b)は,ソースと基板間のPN接合を矢印で表したもので,矢印のついているのが基板電極である. 図5(a),(b)は,ゲートの位置をソース側に移動して,ソースとドレインの区別をつけたものである. 図6(a),(b)は,ソース端子に矢印をつけ,向きでN,Pチャネルを区別をつけたものである.